# **BLACKSMITH:** Scalable Rowhammering in the Frequency Domain

Patrick Jattke ETH Zurich pjattke@ethz.ch Victor van der Veen Qualcomm Technologies Inc. vvdveen@qualcomm.com Pietro Frigo VU Amsterdam p.frigo@vu.nl Stijn Gunter ETH Zurich sgunter@ethz.ch

Kaveh Razavi ETH Zurich kaveh@ethz.ch

Abstract—We present the new class of non-uniform Rowhammer access patterns that bypass undocumented, proprietary in-DRAM Target Row Refresh (TRR) while operating in a production setting. We show that these patterns trigger bit flips on all 40 DDR4 DRAM devices in our test pool. We make a key observation that all published Rowhammer access patterns always hammer "aggressor" rows uniformly. While uniform accesses maximize the number of aggressor activations, we find that in-DRAM TRR exploits this behavior to catch aggressor rows and refresh neighboring "victims" before they fail. There is no reason, however, to limit Rowhammer attacks to uniform access patterns: smaller technology nodes make underlying DRAM technologies more vulnerable, and significantly fewer accesses are nowadays required to trigger bit flips, making it interesting to investigate less predictable access patterns.

The search space for non-uniform access patterns, however, is tremendous. We design experiments to explore this space with respect to the deployed mitigations, highlighting the importance of the order, regularity, and intensity of accessing aggressor rows in non-uniform access patterns. We show how randomizing parameters in the frequency domain captures these aspects and use this insight in the design of Blacksmith, a scalable Rowhammer fuzzer that generates access patterns that hammer aggressor rows with different phases, frequencies, and amplitudes. Blacksmith finds complex patterns that trigger Rowhammer bit flips on all 40 of our recently purchased DDR4 DIMMs,  $2.6 \times$  more than state of the art, and generating on average  $87 \times$  more bit flips. We also demonstrate the effectiveness of these patterns on Low Power DDR4X devices. Our extensive analysis using Blacksmith further provides new insights on the properties of currently deployed TRR mitigations. We conclude that after almost a decade of research and deployed in-DRAM mitigations, we are perhaps in a worse situation than when Rowhammer was first discovered.

### I. INTRODUCTION

A dangerous mistake when designing a mitigation is assuming that attackers will operate the same way after the deployment of the new mitigation. This is especially true for in-DRAM Target Row Refresh (TRR), a selection of defense mechanisms for stopping the ever-worsening Rowhammer effect in the DRAM substrate. Proprietary, undocumented in-DRAM TRR is currently the only mitigation that stands between Rowhammer and attackers exploiting it in various scenarios such as browsers, mobile phones, the cloud, and even over the network [1]–[11]. In this paper, we show how deviations from known uniform Rowhammer access patterns allow attackers to flip bits on all 40 recently-acquired DDR4 DIMMs,  $2.6 \times$  more than the state of the art [12]. The effectiveness of these new non-uniform patterns in bypassing TRR highlights the need for a more principled approach to address Rowhammer.

Existing Rowhammer patterns. Data in DRAM is stored in rows of cells. These cells consist of capacitors that leak charge over time. For preserving the data, the charge needs to be restored by refreshing the cells regularly. However, it is possible to leak charge from these cells with the Rowhammer vulnerability before they have a chance to get refreshed [13]. Existing approaches trigger Rowhammer by selecting one to many different "aggressor" rows to hammer [1], [12], [14]. These aggressor rows are repeatedly accessed in a short duration before cells get refreshed, causing bit flips in "victim" rows that are adjacent to these aggressors. As an example, the doublesided Rowhammer access pattern sandwiches a victim row with two aggressor rows, maximizing charge leakage in the victim row. To leak as much charge from victim rows as possible, such patterns hammer aggressors as often as possible before their victims have a chance to get refreshed.

**Target Row Refresh.** Target Row Refresh (TRR) is an umbrella term for hardware mitigations against the Rowhammer vulnerability, with recent variants operating entirely inside DRAM chips [12]. At a high level, TRR aims to detect rows that are frequently accessed (i.e., hammered) and refresh their neighbors before their charge leak results in data corruptions. The challenge is finding the frequent items in a stream of DRAM accesses. However, as precise frequent item counting is expensive in hardware, TRR implementations try to estimate the frequent items (i.e., the aggressors). Recent work shows that by increasing the number of aggressors, certain implementations of TRR are unable to keep track of all aggressors and corruptions resurface [12]. A majority of TRR implementations (roughly 70%), however, remain secure since they can detect all aggressors given that they are hammered *frequently enough*.

**Non-uniform Rowhammer patterns.** We make the key observation that prior Rowhammer attacks always access aggressors *uniformly*. From a frequent item counting perspective, this is a straightforward case for estimating frequent items. However, there is, of course, no need for attackers to hammer in the space where TRR implementations operate effectively. Given the increasing (physical) susceptibility of DRAM to Rowhammer [15], aggressors no longer need many accesses: attackers are free to choose from many hammering strategies between the times a victim row is refreshed. While this provides many possibilities to fool the TRR's estimation of the frequent items, at the same time, it creates a problem for attackers since the search space for *non-uniform* patterns is huge.

We design a series of experiments that start by randomizing

the patterns and gradually discovering the essential properties that make them successful. This exploration ultimately results in a set of parameters for constructing non-uniform patterns that can effectively explore the weaknesses in existing TRR mechanisms. Notably, we find three *temporal* properties, namely *order*, *regularity*, and *intensity*, play a crucial role in constructing non-uniform patterns that can escape various TRR mechanisms.

Rowhammering in the frequency domain. To capture these temporal parameters, we propose constructing non-uniform patterns in the frequency domain. Signal properties such as phase, frequency, and amplitude conveniently map to the parameters that are important in exploring the blind spots of TRR. Based on this insight, we build *Blacksmith* — a scalable Rowhammer fuzzer capable of generating access patterns by randomizing parameters in the frequency domain for randomly selected aggressors. In contrast to previous work [12], our novel patterns are highly complex, making it difficult for humans to explore manually. Furthermore, our scalable fuzzing-based approach makes it easy to test a large number of DRAM devices against Rowhammer, without the need for time-consuming reverse engineering. On top of generating non-uniform patterns, we can distinguish interesting DRAM-dependent temporal properties by analyzing patterns that triggered bit flips.

Our evaluation shows that Blacksmith can generate patterns that can trigger bit flips on all 40 recently purchased DRR4 DIMMs from the three major DRAM vendors (Samsung, Micron, and Hynix), a factor of  $2.6 \times$  more than state-of-the-art many-sided patterns [12]. We also demonstrate the effectiveness of these patterns on 16 out of 19 Low Power DDR4X devices. These results show that instead of obscure TRR mitigations, we need to invest in principled mitigations with clear guarantees. To gain more insights into these non-uniform patterns, we systematically evaluate how Blacksmith converges to the specific values of the different spatial and temporal parameters. Using the bit flips triggered by these patterns, we uncover interesting new properties of deployed TRR mitigations such as the number of aggressors that they track, the importance of the aggressors' addresses, and significant differences in the number of triggered bit flips on different chips of the same device. Furthermore, we reverse-engineer properties of the TRR implementation on one of the Low Power DDRX devices where Blacksmith could not trigger bit flips and show how a different configuration of Blacksmith could trigger bit flips on these devices.

Contributions. We make the following contributions:

- (1) We present novel non-uniform Rowhammer patterns that make it difficult for TRR to estimate the potential aggressor rows accurately.

- (2) We design Blacksmith, a new Rowhammer fuzzer that can effectively explore the important parameters of these nonuniform patterns by hammering in the frequency domain.

- (3) We evaluate Blacksmith on 40 DDR4 DIMMs from all three major DRAM vendors, showing that it is possible to trigger bit flips on 100% of them by using non-uniform

patterns. We also show Blacksmith's ability to trigger bit flips on 16 out of 19 LPDDR4X DRAM chips.

(4) We conduct an extensive analysis of the effective patterns and bit flips found by Blacksmith to gain insights on patterns and deployed mitigations. Furthermore, we reverseengineer the TRR mechanism of one of the LPDDR4X devices where Blacksmith could not trigger any bit flips to show how it can better be configured.

**Reproducibility.** To enable reproducibility, we publish the source code of Blacksmith on this URL: https://github.com/comsec-group/blacksmith.

Responsible disclosure. We reported our findings to affected parties by following a responsible disclosure process. In Q1-2021, we initiated the process with the NCSC Switzerland (NCSC-CH). In Q2-2021, NCSC-CH informed affected parties and shared our results with DRAM vendors, OEMs, and cloud providers. In Q3-2021, NCSC-CH sent affected parties an updated version of our work and announced the public disclosure date. In Q4-2021, we have been assigned a CVE (CVE-2021-42114) and publicly disclosed Blacksmith on November 15, 2021. The three DRAM manufacturers (Samsung, SK Hynix, and Micron), Intel, AMD, Microsoft, Oracle, and Google confirmed the receipt of our findings. SK Hynix got in touch with us to discuss the LPDDR4X results. We discussed a possible mitigation with Intel and our findings more in detail with Google. None of the contacted parties informed us of their mitigation plans.

# II. BACKGROUND

This section gives an overview of DRAM, including its internal organization and interaction with the memory controller. We also introduce the Rowhammer attack, widely-deployed mitigations against it, and describe common access patterns.

## A. DRAM Organization

While there are different DRAM types for PCs, servers, and laptops, they share a common organization discussed here.

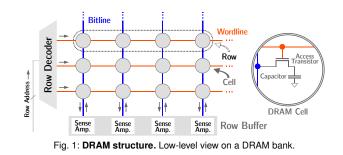

Addressing & Geometry. A DRAM address is composed of a channel, bank, rank, row, and column. Each *channel* is connected to one or multiple DIMMs, of which each can operate independently. A DIMM is equipped with multiple DRAM *chips* that are grouped into *ranks* and these, in turn, consist of multiple *banks* that can operate in parallel [16]. A bank is made of many DRAM cells, of which each contains a capacitor, which stores a single data bit as electrical charge, and an access transistor. These cells are arranged in a twodimensional grid (see Figure 1) and connected row- and columnwise by a *word*- and a *bitline*, respectively. Every bank has a *row buffer*, an array of sense amplifiers connected to the bit lines involved in reading/writing data from/to rows.

DRAM Commands [16]. Before reading or writing data to a DRAM address, the memory controller (MC) puts the associated bank in a precharged state by issuing the PRECHARGE command to DRAM, deactivating the row buffer. Next, the MC issues an ACTIVATE command, after which the requested row is loaded into the row buffer. Now, data can be read (READ) or written (WRITE); both require specifying the targeted column(s) of the loaded row. Additionally, the MC must issue REFRESH commands regularly, on average every 7.8 µs (the *refresh interval* or tREFI) [17], to preserve a cell's value since the capacitors leak charge over time [18]. The REFRESH only refreshes a small subset of rows at a time, which are determined by the DRAM chip, based a row's last refresh time. Related to that is the *retention time*, typically 64 ms in DDR4 [18], [19], the minimum time that DRAM cells must be able to hold data without losing information.

## B. Rowhammer

While the industry has been aware of the Rowhammer vulnerability in DRAM since at least 2012 [20], Kim et al. [13] studied the problem rigorously for the first time in their seminal paper in 2014. They observed that commodity DRAM chips from all major vendors suffer from disturbance errors induced by repeatedly opening (ACTIVATE) and closing (PRECHARGE) a DRAM row (i.e., *aggressor* row) in a short period of time. This action causes some cells in neighboring rows (i.e., *victim* rows) to leak charge at a faster pace than usual. Consequently, these cells can no longer retain their charge for the period they are supposed to before the cell is refreshed, resulting in their bits flipping.

The Rowhammer attack attracted much attention due to its devastating impact on systems security. Follow-up research showed how Rowhammer can be used to compromise users via JavaScript [2], [3], [8], [11], in the cloud [4], [5] on mobile phones [6], [7], and even over the network [9], [10].

**Target Row Refresh.** The industry has responded to Rowhammer by deploying a mitigation known as Target Row Refresh (TRR). Frigo et al. [12] analyzed TRR and found that it refers to a variety of different solutions with the recent variants all operating inside the DRAM chips. They further show that in-DRAM TRR tries to detect which rows are being hammered using a *sampling* mechanism and internally refreshes their victims before these receive their regular refresh. An ideal TRR sampler needs to keep track of every row that receives an ACTIVATE command but doing so is expensive in hardware. Instead, existing TRR mechanisms estimate the rows that are activated most often. The TRRespass fuzzer [12] shows gaps in this estimation by increasing the number of aggressor rows, causing Rowhammer bit flips to resurface on roughly 30% of modern DDR4 DIMMs. The question that we are trying to

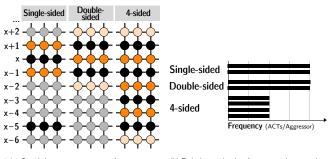

(a) Spatial arrangement of aggressor rows () and victim rows () in DRAM memory.

(b) Relative activation frequency, i.e., number of ACTIVATEs per aggressor in a Rowhammer pattern.

Fig. 2: **Common Rowhammer access patterns.** Overview of the most common Rowhammer access patterns from prior work.

answer in this paper is whether there are more effective ways of discovering gaps in the estimation of aggressor rows.

Rowhammer Access Patterns. We use the term pattern to describe memory access sequences and denote patterns as being effective when they can trigger bit flips. In search of effective patterns for more DIMMs, we must understand how existing instances work. Figure 2a shows the three common Rowhammer access patterns. In the original work [13], the authors used two far apart aggressor rows for hammering, later termed as single-sided because, from the victim row's point of view, their charge is being leaked from one side. Later, Seaborn and Dullien [1] showed that if a victim row is sandwiched by two aggressors, it increases the chance of bit flips (i.e., doublesided). Frigo et al. [12] introduced *n*-sided Rowhammer, where n refers to n-1 victims being hammered by n aggressors from both sides. Figure 2a shows an example with n = 4. The recent SMASH attack [11] shows that it can trigger bit flips in JavaScript by synchronizing n-sided patterns with the DRAM REFRESH command. Our experiments with SMASH patterns, as discussed in Appendix A, show that while aligning with REFRESH increases the number of effective patterns found on certain DIMMs, overall, it does not compromise TRR on more devices than the original *n*-sided patterns.

We make a key observation that the aggressors in all these previous patterns are hammered *uniformly* as shown in Figure 2b. While hammering uniformly maximizes the chance of triggering a Rowhammer bit flip, since it maximizes the frequency in which the aggressors are hammered, it is also the easiest case for TRR to estimate the rows that are accessed the most (i.e., hammered). Given the increasing degree of vulnerability to Rowhammer, the aggressors no longer need to be hammered as frequently as possible, and a significantly smaller number of accesses is enough to trigger Rowhammer [15]. This provides an opportunity to better exercise the TRR's estimation of aggressor rows by hammering *non-uniformly*. This paper explores the design of non-uniform patterns against in-DRAM TRR.

## **III. PROPERTIES OF EFFECTIVE NON-UNIFORM PATTERNS**

While non-uniform access patterns will likely make it more challenging for TRR to estimate the aggressors, at the same time, they are challenging to craft due to the large design space. Let us consider the possible number of activations in a tREFI ( $\approx 100$  accesses), so we end up with  $\approx 819$  k possible activations between two (victim) row refreshes, where each could potentially be used to hammer our aggressors. Assuming that we need to hammer 10 k times, it gives us more than  $6.7 \times 10^{23447}$  possibilities to distribute our double-sided aggressor accesses (see Appendix C for details). As this is impractically large, we explore the important properties of effective non-uniform patterns to reduce the size of this search space.

One possibility is to reverse-engineer specific details of various TRR implementations, as has been done in concurrent [21] and earlier work [12]. This is a time-consuming process and needs to be repeated on new devices given that vendors tend to change their implementations [12]. Instead, our goal here is to determine the generic properties of existing TRR implementations. For this purpose, we conduct a series of experiments on DIMMs  $A_{10}$  and  $B_2$  of the two major vendors in our test pool. We later show how these discovered properties can help in triggering bit flip on other DIMMs from the same vendors as well in devices from other vendors.

We start exploring non-uniform patterns by randomizing the number of aggressors being hammered and their location (Section III-A). To limit the search space, we try to answer questions such as *when* we should hammer an aggressor and for *how long*. We first answer these questions for patterns that fit within a REFRESH interval (Section III-B) and later extend our search to larger patterns (Section III-C). After we understand the properties of successful patterns, we discuss how we can capture these properties when generating effective non-uniform access patterns (Section III-D).

#### A. Can non-uniform access patterns bypass mitigations?

We design an experiment to explore the effectiveness of nonuniform patterns. In this experiment, we assess the importance of non-uniformity by considering two extremes in the design space: (i) adding *some* randomness to *n*-sided patterns and (ii) creating randomized patterns.

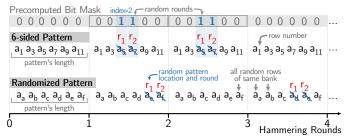

In the first experiment (i), we introduce non-uniform aggressor accesses (i.e., accesses at random times) into common n-sided patterns by accessing selected aggressors more or less often than all others. This means, we access a randomly picked double-sided aggressor pair at random times during the regular accesses of an n-sided pattern<sup>1</sup>.

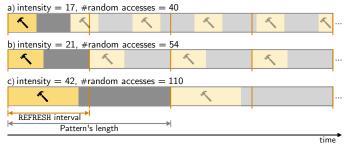

The naive approach for implementing such random accesses would be using conditional branching based on some random value. However, the CPU might speculatively execute the wrong branch, leading to unwanted memory accesses. Therefore, we rewrite our branching into a statement that targets different memory locations depending on the condition's value. As depicted in Figure 3, we precompute a bit mask that decides when and how often our aggressor pair should be hammered. This bit mask is computed based on existing work [15] that showed between 10 k and 147.5 k ACTIVATES (*Hammer*

Fig. 3: Non-uniform patterns experiment. (i) We take a *n*-sided pattern (e.g., n = 6) and based on a precomputed bit mask, randomly replace accesses to a randomly picked double-sided aggressor pair  $r_1, r_2$ . (ii) We create a randomized pattern and hammer a randomly-picked double-sided aggressor pair  $r_1, r_2$  at random times.

*Count*) are required on modern DDR4 devices to trigger bit flips. Ideally, this value should be as small as possible to reduce the chance of detection by TRR, yet large enough to cause a bit flip. As we cannot determine this value for our PC-DDR DIMMs, we randomly pick a value in between 10 k and 147.5 k for each pattern. While hammering the pattern, we then use the bit mask to offset an array that points to part of our *n*-sided pattern or our randomly-picked double-sided aggressor pair.

In experiment (ii), we follow the same methodology to access a selected double-sided aggressor pair non-uniformly; however, instead of a *n*-sided pattern as a basis, we now randomize the pattern's accesses. Note that these random accesses are spread over the same bank as our aggressors, i.e., there are no fixed distances in-between aggressors like in *n*-sided patterns. Similarly as in experiment (i), we use patterns of length  $n \in$ [2, 32] but we replace aggressors by our double-sided aggressor pair at random locations of the pattern. This makes all aggressor accesses in our pattern non-uniform.

We extended TRRespass [22] by these two new ways of creating patterns and try these patterns as well as the original n-sided patterns on all DIMMs of our test pool (see Appendix B) for 6 h. To see if a pattern is successful, we check all rows next to accessed rows for bit flips. The randomized approach was the most successful and could trigger bit flips on 37.5% of all devices in our test pool, followed by n-sided patterns (35%), and n-sided patterns with random accesses (27.5%). Considering all three approaches together, we observed bit flips on 20 of 40 DIMMs (50%). From these 20 DIMMs, there are 8 DIMMs where all three approaches triggered bit flips and 6 DIMMs where one (or both) of the two non-uniform approaches succeeded. Table VII in Appendix D provides more detailed results from these experiments.

These experiments confirm our assumption that there are DIMMs where we need non-uniform patterns to bypass the mitigation. This shows that non-uniformity is a promising concept for finding effective Rowhammer access patterns on more devices.

**Observation** (O1). Non-uniform accesses can lead to effective patterns on DIMMs where previous n-sided patterns could not trigger any bit flips.

However, there are also three opposite cases where only pure

<sup>&</sup>lt;sup>1</sup>with a randomly picked number of aggressors  $n \in [2, 32]$ , an aggressor intra-distance  $d \in [0, 16]$ , and an aggressor intra-distance  $v \in [1, 4]$ .

Fig. 4: Offset & intensity experiment. Systematic probing of aggressor offsets 0...N - 2 for a pattern of length N.

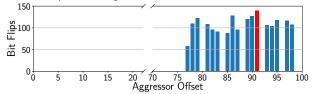

Fig. 5: **Aggressor offset.** Observed bit flips on  $A_{10}$ , over ten probed locations, at which we place aggressors at different offsets in the pattern (N = 100). Using an offset of 91 (red) triggers the most (140) bit flips.

n-sided patterns are effective; this indicates that these simple approaches for pattern generation are not effective enough. Besides that, we observe that our pattern search space is not optimal yet: using n-sided patterns as a base seems to be too restrictive, whereas the random approach creates an enormous search space that cannot be explored in sufficient depth within a reasonable time. Therefore, we aim to identify parameters of effective patterns that allow us to guide pattern generation and, as such, reduce the search space.

# B. When should we hammer an aggressor and for how long?

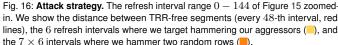

Prior work [11], [12] suggests that in-DRAM TRR acts at the same time of a REFRESH. Based on this, we aim to explore the parameters of effective non-uniform patterns within two consecutive REFRESH commands, i.e., a refresh interval.

To verify *when* we should hammer, we design an experiment where we randomly choose a double-sided aggressor pair  $(a_1, a_2)$  and generate a pattern of length N, where N corresponds to the number of memory accesses that fit inside a refresh interval (determined experimentally beforehand). For each possible offset t = 0, ..., N - 2 in that we can place the two aggressors, we craft a pattern as follows: the aggressors  $a_1$  and  $a_2$  are placed at position t and t+1 in the pattern, respectively, and the remaining  $N - |\{a_1, a_2\}| = N - 2$ accesses, (i.e., positions  $0 \le i < N$  for  $i \notin \{t, t+1\}$ ) are filled up by accesses to random rows in the same bank as  $a_1$  and  $a_2$ . This is depicted in Figure 4: the pattern's aggressor accesses are highlighted in yellow and the random accesses in grey. We repeat hammering each pattern for one million rounds, i.e., long enough to see bit flips even with strong DRAM cells [15]. We note that the rows are randomly picked for each offset (including the aggressors) in each iteration of the experiment. For improving the reliability, we repeat the experiment ten times on different locations (i.e., DRAM rows). To ensure that these patterns remain inside the refresh interval, at the end of each round, we access two random rows from the same bank repeatedly until we observe a peak in the access time, which signals that a REFRESH happened.

Figure 5 depicts the results of our experiment for  $A_{10}$ , aggregated over ten DRAM locations. The *best pattern*, i.e.,

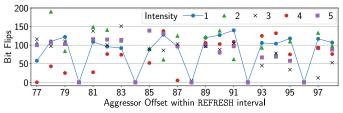

Fig. 6: **Hammering intensity.** Number of observed bit flips when repeating hammering the aggressors with different intensity (1–5), accumulated over 10 different locations on  $A_{10}$ . Hammering with an intensity of two, starting from offset 78, triggers the most (190) bit flips.

the pattern that triggered the highest number of bit flips (red bar), starts at offset 91 and generates 140 bit flips. We can see that an arbitrarily chosen aggressor offset may lead to no bit flips because the TRR sampler on this device considers the first accesses in a refresh interval, similar to the observations reported in earlier work [12]. These results suggest that towards the end of the refresh interval, only certain accesses (at offsets  $80, 84, \ldots, 96$ ) are sampled. Hence, we can trigger bit flips by hammering at specific times in the last  $\approx 23\%$  of the refresh interval (i.e., offsets 77 - 98). The number of bit flips that we observe in this range is, on average, higher than for all other possible offsets within a REFRESH interval. From that we conclude that our assumption is correct: carefully choosing *when* to access aggressors is significant for maximizing effectiveness.

**Observation (O2).** Inserting aggressors at the "right" location in a pattern enables them to bypass the mitigation.

A natural follow-up question from this result is whether hammering our aggressor pair with greater intensity (i.e., more than only once successively) increases the number of observed bit flips. More bit flips are favorable for attacks as they typically require bit flips at specific page offsets. Hence, more bit flips increase the attack's success rate. However, accessing an aggressor pair successively too often will likely result in a TRR. To investigate this, we extend our last experiment by repeating hammering each possible pattern offset up to five times for one million rounds in total. This experiment is depicted in Figure 4. We limit the intensity to five because higher intensities do not trigger bit flips anymore.

In Figure 6, we show the results of this experiment. We report observed bit flips within aggressor offset 77 - 98 (derived from the previous experiment, see Figure 5). We can see that for some offsets, an increased hammering intensity leads to more bit flips. For example, starting from offset 78 and successively hammering two times is more effective (190 bit flips) than only a single time (110 bit flips) and also outperforms the best offset hammered only a single time (offset 91, 140 bit flips). As expected, hammering the aggressors for too long triggers a TRR, which results in fewer or no bit flips at all. This strongly indicates that TRR sampling happens at specific offsets (80, 84, 88, ...), but it is not enough for an aggressor row to get sampled only at one of them. For example, we can see that at offset 80 with an intensity of 5, our aggressors are

Random Accesses in Between Aggressor Accesses

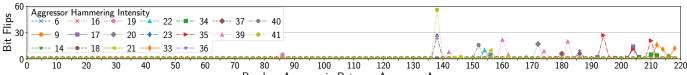

Fig. 8: Hammering duration. Observed bit flips on B<sub>2</sub> for patterns up to three REFRESH intervals, a varying number of random accesses and aggressor hammering intensities. Choosing an offset of 138 with intensity of 41 triggers the most (56) bit flips. We omit intensities without any bit flips.

Fig. 7: **Regularity experiment.** Examples of tested patterns with different intensity and number of random accesses: a pattern smaller than (a) and of equal length to (b) a refresh interval, and (c) one covering two refresh intervals. Opaque regions show the pattern's repetition during execution.

sampled by the mitigation; however, if we use an intensity of 4 starting at offset 79, we also do access an aggressor at offset 80 but we do trigger bit flips. This suggests that the TRR mechanism on this device deploys a counter and we need to get sampled multiple times before a TRR. We conclude from this that there is a *sweet spot* up to which we can increase the intensity to induce more bit flips.

**Observation (O3).** Up to a specific point (*sweet spot*), increasing the hammering intensity leads to more bit flips.

These two properties of effective non-uniform patterns allow us to reduce the search space because the pattern's length of one refresh interval implicitly limits possible offsets and hammering intensities for our aggressors. However, running the same experiment on  $\mathcal{B}_2$ , required a significantly higher hammering intensity to trigger bit flips. We tried intensities up to a whole refresh interval and could trigger only 5 bit flips with an intensity of 19. Not to risk limiting our search space by too much, we will also explore whether larger patterns can be more effective in bypassing certain TRR variants, such as the one employed in  $\mathcal{B}_2$ .

## C. Should our patterns be longer than one refresh interval?

To answer the question of the pattern's length, we design the experiment presented in Figure 7. We first hammer two randomly picked double-sided aggressors with a given intensity and then issue a varying number of alternating accesses to two randomly picked rows. In our experiment, we cover intensities from 1 up to 64 and between 1 and 384 random accesses because they result in patterns of up to  $64 \times 2 + 2 \times 192 =$ 512 accesses, which covers five full refresh intervals. Again, we repeat the experiment for each combination ten times on different DRAM locations and check the rows around the double-sided aggressors for bit flips. Unlike before, we do not synchronize with the REFRESH anymore since our patterns now grow beyond a single refresh interval. This approach allows us to investigate how access intensity and regularity affect a pattern's effectiveness.

Figure 8 shows the experiment's result for intensities where we observed bit flips. As the number of observed bit flips decreased if we issued more than 200 random accesses inbetween, we focus here on two refresh intervals only. In contrast to the earlier observation on  $A_{10}$  (Section III-B), the DIMM  $B_2$  considered here requires a higher intensity ( $\geq 6$ ) to trigger any bit flips due to its different TRR implementation. The plot shows notable differences in the number of bit flips for specific pattern lengths. Interestingly, there are cases where we hammered almost the whole refresh interval ( $\approx 85$  accesses) without being captured by the mitigation. For example, with hammering intensity of 41 and offset of 138, we first issue  $41 \times 2$  aggs. = 78 aggressor accesses (i.e., almost a whole REFRESH interval), followed by 138 random accesses.

We conclude with two points from these findings. For an aggressor pair to successfully trigger bit flips, (1) it should not be hammered in certain (long) periods, and (2) when it is hammered, it should be with high intensity, even up to a whole refresh interval. These results naturally imply that we need to consider patterns larger than a single refresh interval.

**Observation (O4).** Hammering aggressors with a high intensity at specific points inside multiple refresh intervals allows us to bypass the mitigation more effectively.

## D. How can we generate new patterns based on these insights?

In this section, we showed that non-uniformity allows finding effective patterns where previous approaches failed (O1) and that it is crucial to carefully choose when, within the pattern, to issue memory accesses to the aggressors (O2). We further discovered that the number of successive hammering repetitions can increase the number of bit flips (O3) and that long patterns, covering multiple refresh intervals, are necessary to discover patterns triggering bit flips on certain DIMMs (O4).

We leveraged these four observations to design and implement Blacksmith, a new blackbox Rowhammer fuzzer. Blacksmith generates patterns consisting of aggressors that are placed in the pattern using concepts from the frequency domain, such as *phase*, *amplitude*, and *frequency*. This enables us to distinct aggressors by expressing when we access them (*phase*), how often we repeat accessing them successively (*amplitude*), and how their accesses are distributed over time (*frequency*). By fuzzing these properties, we can compose patterns that stress TRR mitigations to trigger bit flips successfully. Our approach finds parameters efficiently by probing multiple

Fig. 9: **Blacksmith's architecture.** Overview of Blacksmith's main components, their interaction, and execution order (1-5).

{phase, amplitude, frequency} sets for different aggressors in a single pattern. This eliminates the need to explicitly select aggressors given that now the entire pattern is comprised of potential aggressors, some fooling the mitigations while the others effectively hammering. To the best of our knowledge, Blacksmith is the first fuzzer that uses this novel strategy for generating non-uniform Rowhammer patterns.

## IV. BLACKSMITH

We now describe the design and implementation of Blacksmith. We first give a high-level overview of Blacksmith's architecture (Section IV-A), followed by describing how Blacksmith generates Rowhammer patterns, including a formalization of the underlying concepts (Section IV-B). After that, we introduce Blacksmith's parameter-tracking mode that uses bit flips as a feedback mechanism to learn parameters of effective patterns (Section IV-C). Finally, we provide selected implementation details (Section IV-D).

## A. High-Level Overview

Figure 9 depicts Blacksmith's components. The Pattern Generator 1 implements our non-uniform access patterns, which randomizes the temporal aspects of the aggressors inside the pattern (i.e., when within a pattern, for how long successively, and how often aggressors are accessed). The Aggressor Mapper 2 maps aggressors to DRAM locations, i.e., assigns each aggressor of a temporal pattern to a DRAM address by using known bank/rank address functions [11], [23]. In this step, aggressors can either be distributed equidistantly over the same DRAM bank (i.e., same number of rows in between) or randomly placed with one row in between aggressors that target the same victim. These mapping parameters are also randomized during fuzzing. The mapper then derives the virtual addresses corresponding to all hammered rows and passes them to the *Code Generator* **3** to just-in-time (JIT) compile the hammer instructions into an executable code page. For the same reason as in Section III-A, we compile access patterns to avoid conditionals (e.g., if-else) during pattern execution as branches can be executed speculatively, resulting in unwanted memory accesses, and thus "break" our pattern's access order. Also, it allows us to determine where we need to serialize memory reads and flushes using fences. We follow a flush-early and fence-late strategy by flushing aggressors from the cache immediately after accessing them and fencing immediately before accessing them again to minimize the performance impact of serialization. The *Executor* **4** then runs the compiled code page to execute the pattern for multiple refresh windows (i.e., multiple 64 ms). To ensure that we keep accessing rows with their defined frequency, we synchronize accesses with the REFRESH at the beginning of each pattern's repetition (similar to [11]). Finally, the *Memory Scanner* **5** verifies if the random data pattern, written before to memory, changed during hammering. Because all pattern's aggressors can potentially trigger bit flips, the Memory Scanner checks two rows around each of them for flipped bits; and if it finds any flips, it reports them and restores the original data pattern. We then either (i) hammer the same pattern with the same mapping again on a different DRAM location (3-5), (ii) hammer the same pattern with a new mapping (2-5), (iii) or generate a new pattern and repeat the whole procedure (1-5). Probing different locations is required because we could have been unlucky and tried a pattern on a memory region where cells are less vulnerable, thus resulting in no bit flips. The Parameter Manager and the DRAM Inspector are two supporting components. The Parameter Manager defines fuzzing parameters, their valid value ranges, and samples values from these ranges. The DRAM Inspector loads the proper DRAM address functions (derived from a DIMM's number of ranks as all our evaluation systems are equal) and determines required DIMM-specific information, such as the number of possible ACTIVATEs in a refresh interval.

#### B. Frequency-Based Patterns

Blacksmith crafts access pattern by considering their two dimensions separately: the temporal dimension, which describes *when* we access a row, and the spatial dimension, which defines *where* in memory we hammer (i.e., bank and row). Our *non-uniform access patterns* focus on the temporal dimension discussed next. We consider the spatial dimension by testing a crafted frequency-based pattern on three different (randomly chosen) memory locations as the vulnerability of different DRAM cells may vary [15].

**Capturing temporal properties.** We use a terminology inspired by the frequency domain as composing signals with different frequencies can be used as an analogy to crafting a Rowhammer access pattern with aggressors of different frequencies.

First, we generalize the idea of aggressors by defining the notion of an *aggressor tuple*  $\mathbb{A}_k = (a_1, a_2, \dots, a_k)$ , i.e., an ordered access sequence of k aggressors. Our pattern's aggressors are not associated with specific DRAM locations but we *map* them later to specific DRAM rows. For example, in the case of  $\mathbb{A}_2$ , we could map them like a double-sided aggressor pair. Multiple such aggressor tuples fill up a Blacksmith access pattern to improve the fuzzer's efficiency while exploring the parameter space.

Each aggressor tuple  $\mathbb{A}_k$  has three characteristics: a *frequency*, a *phase*, and an *amplitude*. The *frequency* f defines how often the aggressor tuple  $\mathbb{A}_k$  is accessed within a pattern. The *phase*  $\phi$  defines *when* from the start of the pattern a specific aggressor tuple  $\mathbb{A}_k$  will be executed. The *amplitude*  $\hat{u}$

|                          | $f = \frac{1}{2}$      | Ļ                                                     |                        |

|--------------------------|------------------------|-------------------------------------------------------|------------------------|

| 1 <sup>st</sup> Period   | 2 <sup>nd</sup> Period | 3 <sup>rd</sup> Period                                | 4 <sup>th</sup> Period |

| $a_1 a_2 a_1 a_2$        |                        | $\mathbf{a}_1 \mathbf{a}_2 \mathbf{a}_1 \mathbf{a}_2$ |                        |

| $\phi = 2$ $\hat{u} = 2$ |                        | <i>T</i> =8                                           |                        |

Fig. 10: **Parameters of pattern generation.** Example showing an aggressor tuple  $\mathbb{A}_2 = (a_1, a_2)$  with  $(f, \phi, \hat{u}) = (\frac{1}{2}, 2, 2)$  and  $\mathcal{T} = 8$ .

Table I: **Blacksmith's parameter** setup. For each pattern, we choose a number of aggressor tuples and refresh intervals (which results in the pattern's length N). For each aggressor tuple, we pick a number of aggressors, a phase, an amplitude, and derive a frequency from the base period. The amplitude is limited by  $ACT_{tREF}$ , the number of possible activations in a REFRESH interval.

| Parameter                                | Range                                                                       | Sampling Unit   |

|------------------------------------------|-----------------------------------------------------------------------------|-----------------|

| #Aggressor tuples                        | [8, 96]                                                                     | Pattern         |

| #Refresh intervals                       | [1, 16]                                                                     | Pattern         |

| #Aggressors                              | [1, 2]                                                                      | Aggressor tuple |

| Base period                              | [4, N]                                                                      | Aggressor tuple |

| Phase                                    | [1, N]                                                                      | Aggressor tuple |

| Amplitude<br>– for $\mathcal{B}_{2,8,9}$ | $[1, \text{ACT}_{\text{tref}}]$<br>$[1, 4 \times \text{ACT}_{\text{tref}}]$ | Aggressor tuple |

describes for *how long* we should hammer a specific tuple, i.e., the number of consecutive hammering repetitions of  $\mathbb{A}_k$ .

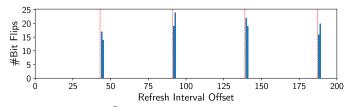

**Building a pattern.** Blacksmith combines multiple aggressor tuples  $\mathbb{A}_k$  to form an access pattern. For intertwining these  $\mathbb{A}_k$  effectively, we define a global parameter that aids the construction: the *base period*. The *base period*  $\mathcal{T}$  defines (and limits) the frequency of an aggressor tuple.

We depict the pattern creation in Figure 10. Before starting to fuzz, assume we determined that we can issue 64 accesses in a refresh interval, and we want our pattern to cover four refresh intervals (i.e.,  $4 \times 64 = 256$  accesses). As a result, we can choose any of  $\{2, 4, \ldots, 256\}$  as the base period. Let us pick 8 so that the frequency f of any aggressor tuple is now a multiple (or divisor) of  $\mathcal{T} = 8$ . For instance, if f = 1we execute the aggressor tuple once every base period, while if f = 2/8 we execute it every 4 (= 8/2) base periods. In Figure 10 we fill the pattern with an aggressor tuple  $\mathbb{A}_2$  with  $(f = 1/2, \phi = 3, \hat{u} = 2)$  meaning that  $\mathbb{A}_2$  is executed every two base periods (f = 1/2), it is displaced by 2 from the start of the pattern ( $\phi = 2$ ), and the aggressor tuple is always hammered two times sequentially ( $\hat{u} = 2$ ).

Once a tuple is inserted, other aggressor tuples are inserted following the same logic avoiding access slots that are already occupied by previously declared aggressor tuples. For instance, after adding  $\mathbb{A}_2$  above, we cannot introduce another  $\mathbb{A}_2$  with  $\phi = 5$  since such time slot is already filled. We refer the interested reader to Appendix E for a more detailed description of the pattern generation algorithm.

Unlike in previous work (e.g., [12], [13], [24], [25]), all accesses in our patterns can potentially trigger bit flips. That means all rows are treated as *aggressors* as we do not distinguish the rows that are only accessed to bypass TRR. After hammering a pattern, we can measure the distance between accessed rows and flipped rows to estimate the *effective* aggressors, i.e., the ones that most likely caused the bit flip. This property also implies that we need to check for bit flips around every accessed row of a pattern.

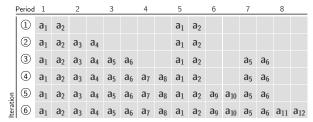

# C. Parameter-Tracking Mode

To understand how Blacksmith parameters impact a pattern's effectiveness, we implemented a parameter-tracking mode. This feature uses a pattern's effectiveness (bit flip count) and rarity (how hard it is to find) in a feedback mechanism to learn which parameter sets are most successful. The parameter-tracking mode starts with a uniform distribution for each parameter and gradually learns, based on the aforementioned indicators, which parameter values work best for specific DIMMs. It uses the feedback to modify the parameter distributions by increasing the probabilities of parameter outcomes that were successful. Using this, we can learn what parameters and values are most important to bypass mitigations. Furthermore, it allows us to derive interesting insights, as we show in Appendix F.

We used our parameter-tracking mode to determine a *golden* set of parameter ranges that can find effective patterns on 37/40 DIMMs of our test pool. For three DIMMs ( $\mathcal{B}_{2,8,9}$ ), we had to slightly increase the amplitude from (up to) one to four refresh intervals. To determine these generic parameters, we performed a 24 h run using large parameter ranges to determine the common ranges based on the discovered effective patterns. Table I shows the final ranges used in our evaluation.

## D. Implementation

Our Blacksmith fuzzer was implemented from scratch in C++11 in around 6.7 k lines of code. It uses several open-source libraries such as *asmjit* [26] for JIT compiling a pattern's accesses and *nlohmann/json* [27] for im- and exporting JSON data (e.g., parameters) needed for analyzing and *replaying* effective patterns, and also for analyzing bit flips. The source code can be found on https://github.com/comsec-group/blacksmith.

# V. EVALUATION

In this section, we evaluate the qualities of non-uniform access patterns. In Section V-A, we describe our test devices and infrastructure. After that, we present our large-scale analysis results on 40 DDR4 DIMMs in Section V-B. In Section V-C, we evaluate how our Blacksmith-generated patterns facilitate Rowhammer exploitation. For completeness, we also evaluate the effectiveness of non-uniform patterns on LPDDR4X in Section V-D. Lastly, we provide concrete examples of Blacksmith patterns in Section V-E.

## A. Hardware and Fuzzer Setup

Our DDR4 DRAM test pool (Appendix B) consists of 40 DIMMs acquired in July 2020 with varying sizes, module speeds, and timings. We cover all three major DRAM vendors, abbreviated by  $\mathcal{A}$  (20×),  $\mathcal{B}$  (10×), and  $\mathcal{C}$  (6×). DIMMs denoted by  $\mathcal{D}$  (4×) do not report their DRAM vendor properly. To show that Blacksmith works in a real-world setup, we do not directly interface with DRAM devices (e.g., FPGA), but we use a traditional PC setup: ten machines equipped with an Intel i7-8700K and running Ubuntu 18.04 LTS (4.15.0). We evaluate LPDDR4X DRAM chips using an in-house, JEDEC-compliant development board that allows us to test DRAM chips from vendors A (6×), B (5×), and C (8×) while operating at 1.5GHz. Similar to previous work [12], we use a pseudorandom, non-repeating data pattern in all our evaluation runs.

# B. Blacksmith Results on DDR4

We aim to evaluate the generality and effectiveness of Blacksmith by answering the question: Is our approach better at finding effective patterns on DIMMs where the state-of-theart cannot trigger any bit flip? To answer this question, we perform a large-scale Rowhammer test and compare Blacksmith results against the data that we obtained using TRRespass [12]. We use the following evaluation methodology: (1) we run Blacksmith for 12 h on each DIMM, i.e., we generate patterns and try each on three different DRAM locations to determine if it triggers bit flips, (2) we "sweep" each effective pattern over (the same) contiguous memory region of 2 MB to determine the best pattern (i.e., most effective) based on the number of observed bit flips, (3) we "sweep" the best pattern over a contiguous memory region of 256 MB to report the best pattern's effectiveness. By "sweeping" we refer to repeatedly moving each row of a pattern by one, hammering the pattern, and checking for flipped bits. For TRRespass, we skip step (2) and use its own definition of the best pattern based on the number of triggered bit flips during the fuzzing run. We remark that the optimality of the *best* pattern is relative to a fuzzing run, and it might be that there are better patterns that Blacksmith could not find within 12 hours.

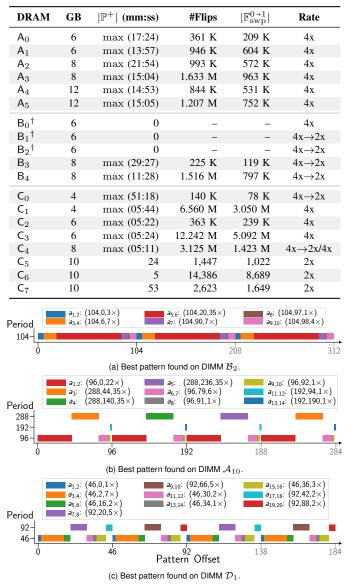

Table II shows the results of our large-scale evaluation run. TRRespass found effective patterns on 15 of 40 tested DIMMs (37.5%), similar to the results from prior work (13 of 42 DIMMs,  $\approx 31\%$ ) [12]. In contrast, Blacksmith found effective Rowhammer patterns on all of our 40 DIMMs (100%).

These results demonstrate Blacksmith's effectiveness and scalability in triggering corruptions — answering our initial question positively. Blacksmith could find effective patterns that trigger, on average,  $87 \times$  more bit flips than TRRespass. We show how this massive increase in the number of bit flips allows for more practical exploitation in Section V-C. Table II also suggests that while there is a trend in DRAM devices from different vendors, there are also outliers.

#### C. Exploitation with Non-Uniform Patterns

We discuss the consequences of these better access patterns found by Blacksmith by analyzing their effect on three existing Rowhammer exploits. For this purpose, we followed prior work [12], [25] and analyzed (i) the first Rowhammer exploit targeting page tables to gain a kernel read/write primitive [1]; (ii) the exploit from Razavi et al. [4] triggering bit flips in public RSA 2048 bit keys to allow their factorization and private key recovery; and (iii) the exploit by Gruss et al. [14] flipping bits on the sudgers.so library to avoid root permission checks.

In our analysis, we briefly summarize each exploit; we refer to the original descriptions [1], [4], [14] for more details. We measure the number of exploitable bit flips when sweeping over a 256 MB chunk of memory and report the mean time to find them by relying on a port of the Hammertime framework [28]. We show the results for all DIMMs in Table III.

In the attack from Seaborn and Dullien [1], the aggressor triggers a bit flip on a page frame number (PFN) in a page table page, "hoping" to pivot its pointer to another (attacker-controlled) page table page. This gives an attacker read/write

access to their page tables, i.e., full access to all physical memory. On a system with 16 GB memory, this results in 23 out of every 64 bit words to be possibly exploitable (i.e.,  $\log_2 16 \, \text{GB} - \log_2 4 \, \text{kB}$ ). This large number of exploitable bits makes it possible to carry out an attack even on a module that manifests very few bit flips; e.g.,  $\mathcal{B}_3$  with only 111 bit flips can be exploited in around 1 hour. The time to find an exploitable bit flips then dramatically decreases for more vulnerable modules, e.g., 22 s on average on  $\mathcal{D}_3$ . The exploit from Razavi et al. [4] gains SSH access to a co-hosted VM by flipping bits on the modulus n of a RSA-2048 public key and factoring the much easier factorable  $n' \ (\neq n)$  to recover the private key. We could identify exploitable bit flips on 30 out of our 40 DIMMs (75%). Finally, Gruss et al. [14] exploit specific bit flips on code pages of the sudoers.so library, stored in the page cache, to gain root privileges. Their opcode flipping technique induces bit flips in cached binary files that often lead to valid opcodes with a different semantic. This technique can break the password verification logic in the sudoers.so. Only 29/(4096 \* 8) bits in a 4 kB page are exploitable for this attack. Still, 15 out of our 40 DIMMs (37.5%) are susceptible to such attack within at most  $38 \min 35$  s ( $A_{12}$ ). These results show how non-uniform patterns largely ease exploitation. In fact, even when considering the more difficult attack (i.e., sudo [14]) we could still build an end-to-end exploit on 15/40DIMMs, which is the total number of DIMMs that TRRespass could trigger bit flips on (see Table II).

Given the large number of bit flip on some devices, we would have expected to see more exploitable bit flips, e.g., in the PTE attack. We investigated this further in Section VI-A, where we show that this is due to the large variance in the number of flips in different chips from the same DIMM.

## D. Blacksmith on LPDDR4X

We evaluate the impact of our non-uniform patterns on LPDDR4X memory. Due to power and die area restrictions, there are key differences compared to regular DDR DRAM that make LPDDR an interesting target for Rowhammer analysis: (i) LPDDR's default refresh window is 32 ms, compared to 64 ms for standard DDR4; (ii) it supports dynamic temperature-based refresh changing through the MR4 Mode Register [29]; and (iii) recent devices deploy on-die ECC [15].

We applied the test methodology outlined in Section V-B to evaluate Blacksmith on 19 LPDDR4X devices. As our LPDDR4X platform is fragile, which makes it difficult to perform longer runs, we had to reduce the run time to 6 h; even then, we had to restart multiple times until we accumulated in total 6 h (this is equivalent as Blacksmith's fuzzing is stateless). Table IV summarizes our results. We observe that Blacksmith can trigger up to two orders of magnitude more bit flips on LPDDR4X compared to DDR4 DRAM, often finding multiple bit flips in every row of every bank. This confirms previous results that indicated the lower Rowhammer tolerance of LP devices, likely a direct result of the area and power restrictions [15]. However, in contrast to DDR4, for some LPDDR4X DRAM modules from vendor  $\beta$  Blacksmith

Table II: **Blacksmith results for DDR4 DRAM compared to TRRespass.** For each DIMM, we report the number of effective patterns found  $(|\mathbb{P}^+|)$ , i.e., patterns that triggered any bit flip during fuzzing; and the total number of bit flips found during fuzzing ( $|\mathbb{F}_{fuzz}^{total}|$ ). For a DIMM's best pattern, we do a sweep over 256~MB and report the same ( $|\mathbb{F}_{swp}^{total}|$ ), plus the number of zero-to-one bit flips ( $|\mathbb{F}_{swp}^{0.4}|$ ). On three DIMMs, marked by  $^\dagger$ , we used an amplitude of up to 4 refresh intervals, see Table I.

Table III: **Analysis of exploitation of our DRAM modules**. Given the bit flips found by Blacksmith's best pattern, we evaluate how many of these bit flips are exploitable (**#Expl.**) when considering three exploits. For each DIMM, we then computed the average time to find an exploitable bit flip (**Time**). We mark (\*) values where a single measurement is available only.

| DIMM                      |                  | Blac                                            | ksmith                                         |                                                                                 |                  | TRRes                                           | pass [12]                                      |                                                                                 | DIMM                       | РТ     | Ъ[]     | RSA    | RSA-2048 [4] |        | sudo [14] |  |

|---------------------------|------------------|-------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------|------------------|-------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------|----------------------------|--------|---------|--------|--------------|--------|-----------|--|

|                           | $ \mathbb{P}^+ $ | $ \mathbb{F}_{\mathrm{fuzz}}^{\mathrm{total}} $ | $ \mathbb{F}_{\mathrm{swp}}^{\mathrm{total}} $ | $\left \mathbb{F}_{\mathrm{swp}}^{0 {\scriptscriptstyle \rightarrow} 1}\right $ | $ \mathbb{P}^+ $ | $ \mathbb{F}_{\mathrm{fuzz}}^{\mathrm{total}} $ | $ \mathbb{F}_{\mathrm{swp}}^{\mathrm{total}} $ | $\left \mathbb{F}_{\mathrm{swp}}^{0 {\scriptscriptstyle \rightarrow} 1}\right $ | DIMIM                      | #Expl. | Time    | #Expl. | Time         | #Expl. | Time      |  |

| $\mathcal{A}_0$           | 47               | 330                                             | 82,183                                         | 41,471                                                                          | 0                |                                                 | _                                              | -                                                                               | $\mathcal{A}_0$            | 7604   | 4s      | 210    | 30s          | 17     | 5m        |  |

| $\mathcal{A}_1$           | 116              | 876                                             | 12,134                                         | 6,095                                                                           | 12               | 12                                              | 5                                              | 5                                                                               | $\mathcal{A}_1$            | -      | -       | 28     | 4m 12s       | _      | -         |  |

| $\mathcal{A}_2$           | 462              | 3,543                                           | 134,702                                        | 68,801                                                                          | 715              | 16,054                                          | 7,404                                          | 4,563                                                                           | $\mathcal{A}_2$            | 9198   | 6s      | 306    | 21s          | 13     | 6m 43s    |  |

| $\mathcal{A}_3$           | 82               | 480                                             | 1,746                                          | 890                                                                             | 326              | 852                                             | 114                                            | 58                                                                              | $\overline{\mathcal{A}_3}$ | 73     | 2m 21s  | 3      | 47m 37s      | -      | -         |  |

| $\mathcal{A}_4$           | 460              | 2,988                                           | 5,132                                          | 2,602                                                                           | 78               | 105                                             | 22                                             | 9                                                                               | $\mathcal{A}_4$            | 214    | 33s     | 7      | 13m 16s      | -      | -         |  |

| $\mathcal{A}_5$           | 42               | 294                                             | 113,190                                        | 57,655                                                                          | 0                | -                                               | -                                              | -                                                                               | $\mathcal{A}_5$            | 99     | 1m 27s  | 269    | 34s          | 12     | 11m 41s   |  |

| $\mathcal{A}_6$           | 102              | 771                                             |                                                | 49,296                                                                          | 4                | 11                                              | 4                                              | 4                                                                               | $\mathcal{A}_6$            | 52     | 2m 12s  | 220    | 32s          | 9      | 11m 55s   |  |

| $\mathcal{A}_7$           | 66               | 450                                             | 32,090                                         | 15,988                                                                          | 0                | -                                               | -                                              | -                                                                               | $\mathcal{A}_7$            | 6043   | 6s      | 69     | 2m 5s        | 8      | 11m 11s   |  |

| $\mathcal{A}_8$           | 83               | 657                                             | 92,660                                         | 46,914                                                                          | 0                | -                                               | -                                              | -                                                                               | $\mathcal{A}_8$            | 64     | 2m 24s  | 184    | 54s          | 15     | 10m 5s    |  |

| $\mathcal{A}_9$           | 349              | 2,256                                           | 4,889                                          | 2,461                                                                           | 14               | 844                                             | 1                                              | 1                                                                               | $\mathcal{A}_9$            | 136    | 28s     | 6      | 9m 45s       | -      | -         |  |

| $\mathcal{A}_{10}$        | 350              | 2,193                                           | 3,051                                          | 1,532                                                                           | 367              | 961                                             | 505                                            | 280                                                                             | $\mathcal{A}_{10}$         | 216    | 24s     | 7      | 12m 4s       | -      | _         |  |

| $\mathcal{A}_{11}$        | 202              | 1,239                                           | 3,171                                          | 1,630                                                                           | 261              | 479                                             | 38                                             | 25                                                                              | $\mathcal{A}_{11}^{10}$    | 197    | 2m 8s   | 13     | 23m 21s      | -      | _         |  |

| $\mathcal{A}_{12}$        | 74               | 576                                             | 43,581                                         | 22,149                                                                          | 0                | -                                               | -                                              | -                                                                               | $\mathcal{A}_{12}$         | 6596   | 7s      | 116    | 55s          | 2      | 38m 35s   |  |

| $\mathcal{A}_{13}$        | 72               | 564                                             | 59,721                                         | 30,320                                                                          | 0                | -                                               | -                                              | -                                                                               | $\mathcal{A}_{13}$         | 4520   | 8s      | 144    | 49s          | 7      | 13m 44s   |  |

| $\mathcal{A}_{14}$        | 51               | 360                                             | 64,083                                         | 32,543                                                                          | 1                | 1                                               | 4                                              | 0                                                                               | $\mathcal{A}_{14}$         | 5172   | 8s      | 151    | 44s          | 7      | 14m 19s   |  |

| $\mathcal{A}_{15}$        | 67               | 516                                             | 52,580                                         | 26,483                                                                          | 0                | -                                               | -                                              | -                                                                               | $\mathcal{A}_{15}$         | 4567   | 8s      | 105    | 1m 3s        | 7      | 14m 7s    |  |

| $\mathcal{A}_{16}$        | 372              | 2,826                                           | 99,552                                         | 51,029                                                                          | 688              | 5,499                                           | 1,450                                          | 983                                                                             | $\mathcal{A}_{16}$         | 6572   | 6s      | 231    | 27s          | 13     | 6m 30s    |  |

| $\mathcal{A}_{17}$        | 425              | 3,189                                           | 138,601                                        | 70,902                                                                          | 711              | 12,196                                          | 3,871                                          | 2,690                                                                           | $\mathcal{A}_{17}$         | 9775   | 3s      | 324    | 11s          | 10     | 5m 1s     |  |

| $\mathcal{A}_{18}$        | 126              | 936                                             | 80,601                                         | 40,876                                                                          | 14               | 14                                              | 1                                              | 1                                                                               | $\mathcal{A}_{18}$         | 11124  | 5s      | 182    | 44s          | 23     | 5m 28s    |  |

| $\mathcal{A}_{19}$        | 107              | 750                                             | 11,599                                         | 5,736                                                                           | 0                | -                                               | -                                              | -                                                                               | $\mathcal{A}_{19}^{10}$    | 832    | 3s      | 20     | 1m 18s       | 3      | 6m 21s    |  |

| $\mathcal{B}_0$           | 9                | 66                                              | 63                                             | 22                                                                              | 0                | -                                               | -                                              | -                                                                               | $\mathcal{B}_0$            | _      | -       | _      | -            | _      | -         |  |

| $\mathcal{B}_1$           | 7                | 39                                              | 506                                            | 256                                                                             | 0                |                                                 | -                                              | -                                                                               | $\mathcal{B}_1$            | 1      | 1h 44m* | 1      | 2h 31m*      | -      | -         |  |

| $\mathcal{B}_2^{\dagger}$ | 9                | 45                                              | 15                                             | 7                                                                               | 7                | 8                                               | 5                                              | 3                                                                               | $\mathcal{B}_2$            | -      | -       | -      | -            | -      | -         |  |

| $\mathcal{B}_3$           | 1                | 6                                               | 111                                            | 58                                                                              | 0                | -                                               | -                                              | -                                                                               | $\mathcal{B}_3$            | 3      | 1h 16m  | -      | -            | -      | -         |  |

| $\mathcal{B}_4$           | 101              | 606                                             | 1,107                                          | 577                                                                             | 0                | -                                               | -                                              | -                                                                               | $\mathcal{B}_4$            | 2      | 1h 27m  | 4      | 34m 7s       | -      | -         |  |

| $\mathcal{B}_5$           | 19               | 105                                             | 14                                             | 6                                                                               | 0                | -                                               | -                                              |                                                                                 | $\mathcal{B}_5$            | -      | -       | -      | -            | -      | -         |  |

| $\mathcal{B}_6$           | 18               | 105                                             | 78                                             | 46                                                                              | 0                | -                                               | -                                              | -                                                                               | $\mathcal{B}_6$            | -      | -       | -      | -            | -      | -         |  |

| $\mathcal{B}_7$           | 4                | 33                                              | 70                                             | 34                                                                              | 0                | -                                               | -                                              | -                                                                               | $\mathcal{B}_7$            | -      | -       | -      | -            | -      | -         |  |

| $\mathcal{B}_8^\dagger$   | 4                | 21                                              | 258                                            | 131                                                                             | 0                | -                                               | -                                              | -                                                                               | $\mathcal{B}_8$            | -      | -       | 1      | 26m 50s*     | -      | -         |  |

| $\mathcal{B}_9^{\dagger}$ | 40               | 234                                             | 1,223                                          | 625                                                                             | 0                | -                                               | _                                              | _                                                                               | $\mathcal{B}_9$            | 3      | 1h 3m   | -      | -            | -      | -         |  |

| $\mathcal{C}_0$           | 1                | 6                                               | 26                                             | 16                                                                              | 0                | -                                               | -                                              | -                                                                               | $\mathcal{C}_0$            | 1      | 2h 8m*  | -      | -            | -      | -         |  |

| $\mathcal{C}_1$           | 16               | 105                                             | 28                                             | 8                                                                               | 0                | -                                               | -                                              | -                                                                               | $\mathcal{C}_1$            | -      | -       | -      | -            | -      | -         |  |

| $\mathcal{C}_2$           | 82               | 531                                             | 2,551                                          | 1,242                                                                           | 0                | -                                               | -                                              | -                                                                               | $\mathcal{C}_2$            | 1      | 1h*     | 3      | 59m 39s      | -      | -         |  |

| $C_3$                     | 6                | 36                                              | 636                                            | 296                                                                             | 0                | -                                               | -                                              | -                                                                               | $\mathcal{C}_3$            | -      | -       | -      | -            | -      | -         |  |

| $\mathcal{C}_4$           | 31               | 213                                             | 769                                            | 385                                                                             | 0                | -                                               | -                                              | -                                                                               | $\mathcal{C}_4$            | 4      | 59m 19s | 2      | 2h 5m        | -      | -         |  |

| $C_5$                     | 23               | 150                                             | 1,028                                          | 516                                                                             | 0                | _                                               | _                                              | _                                                                               | $\mathcal{C}_5$            | -      | _       | 1      | 4h 2m*       | _      | -         |  |

| $\mathcal{D}_0$           | 26               | 186                                             | 10,646                                         | 5,329                                                                           | 0                | -                                               | -                                              | -                                                                               | $\mathcal{D}_0$            | 5202   | 4s      | 23     | 3m 43s       | 4      | 19m 56s   |  |

| $\mathcal{D}_1$           | 37               | 249                                             | 6,655                                          | 3,406                                                                           | 3                | 3                                               | 0                                              | -                                                                               | $\mathcal{D}_1$            | 4      | 19m 33s | 15     | 5m 25s       | -      | -         |  |

| $\mathcal{D}_2$           | 3                | 12                                              | 2,030                                          | 1,008                                                                           | 0                | -                                               | -                                              | -                                                                               | $\mathcal{D}_2$            | 135    | 40s     | 6      | 11m 41s      | -      | -         |  |

| $\mathcal{D}_3$           | 41               | 276                                             | 6,797                                          | 3,475                                                                           | 8                | 8                                               | 1                                              | 1                                                                               | $\mathcal{D}_3$            | 760    | 22s     | 32     | 5m 49s       | -      | -         |  |

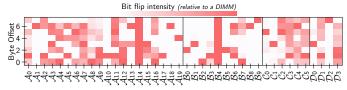

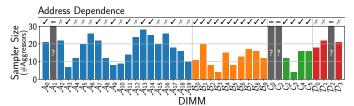

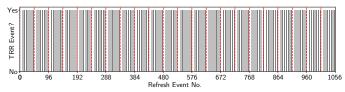

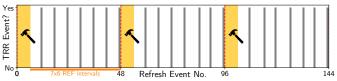

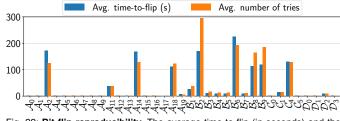

| Σ                         | 4,133            |                                                 | 1.168 M                                        |                                                                                 | 3,209            |                                                 | 13,425                                         |                                                                                 |                            |        |         |        |              |        |           |  |